EECS151 RISC-V FPGA

Jan 1, 2024

·

1 min read

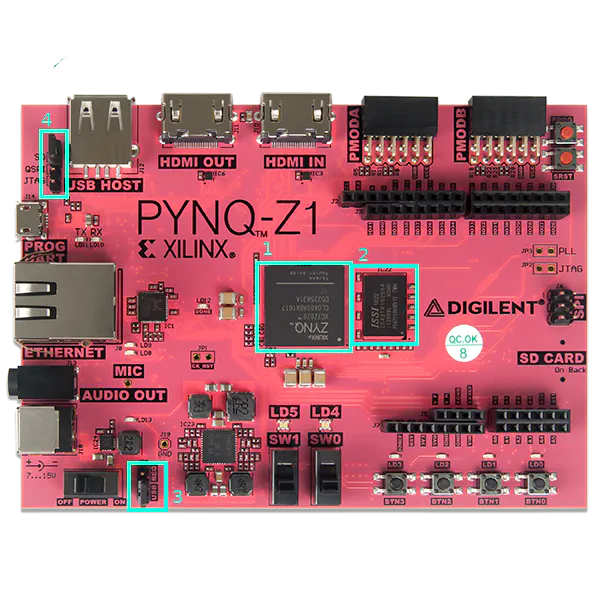

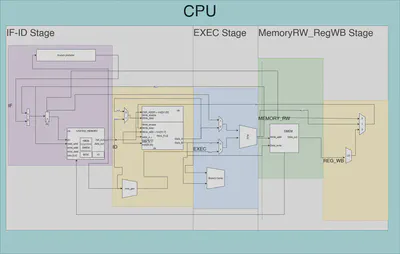

I implemented a 3-stage pipelined RISC-V CPU with the Verilog HDL which is tested an AMD Xilinx PYNQ-Z1 board with a core clock frequency of 75MHz.

The CPU supports the RV32I ISA as well as a subset of CSR instructions. The modifications made to the CPU that is different from the CS61CPU project are:

- It is a synchronous-memory CPU, which means that the CPU has to prefetch instruction during the IF stage.

- It includes a bunch of IO-mapped memory addresses that can be used to detect button presses, control LEDs, and control the audio output.

- It includes an memory-mapped UART module that can be used to communicate with the host computer. A simple BIOS program provided by the class can be used to communicate with the host computer and write programs to the memory. Then the CPU can execute the program.

- It includes an always-taken branch predictor.